# ポストムーア時代を切り拓く設計検証技術

增田 豊(名古屋大学大学院情報学研究科)

# ムーアの法則とは源泉の異なる、新原理コンピューティングの開拓に挑戦!

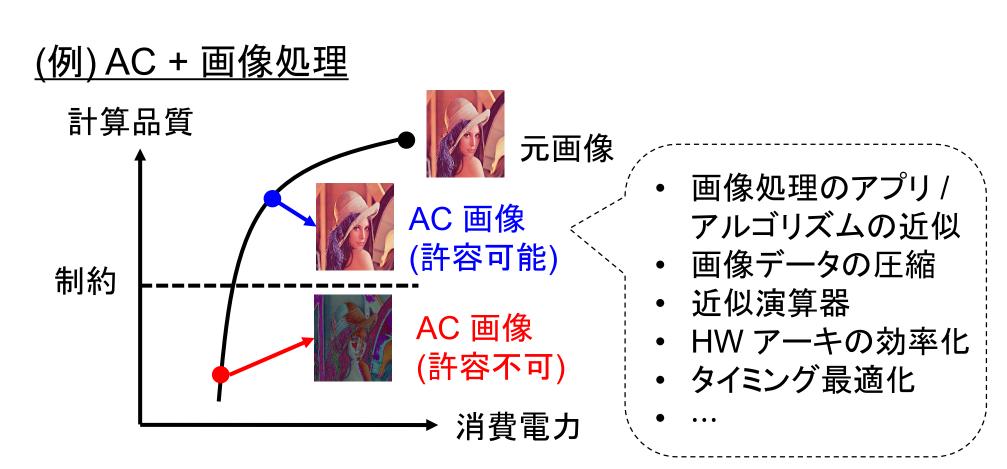

# 近似コンピューティング (AC)

「品質」の制約下で、計算方法を近似

- 近似対象: SW から HW まで横断

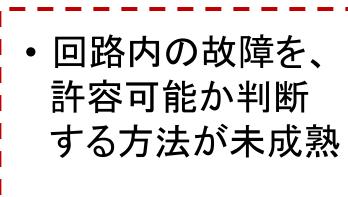

# 目的: AC 回路の設計検証技術の確立

• 従来の CAD (Computer-Aided Design) ✓HW 上の全パスが機能的・タイミング的に正しく動作する前提

→ AC 回路にはそのまま適用できない

計算メカニズムの ブラックボックス性 (例. 機械学習)

#### 研究対象:

#### 設計から検証まで一貫

- AC の効率を高める 設計技術

- AC 回路の性能評価技術、 設計最適化への還元法

- 設計後 AC 回路の正当性 を検証する技術

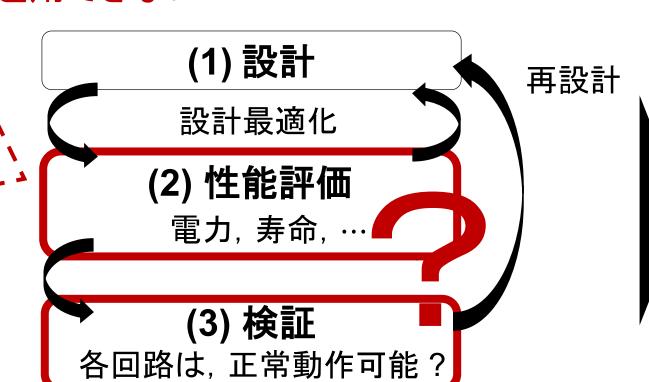

### AC回路の省電力設計技術

提案: BWS (ビット幅削減) と CPI (クリティカルパス・アイソレーション) の協調

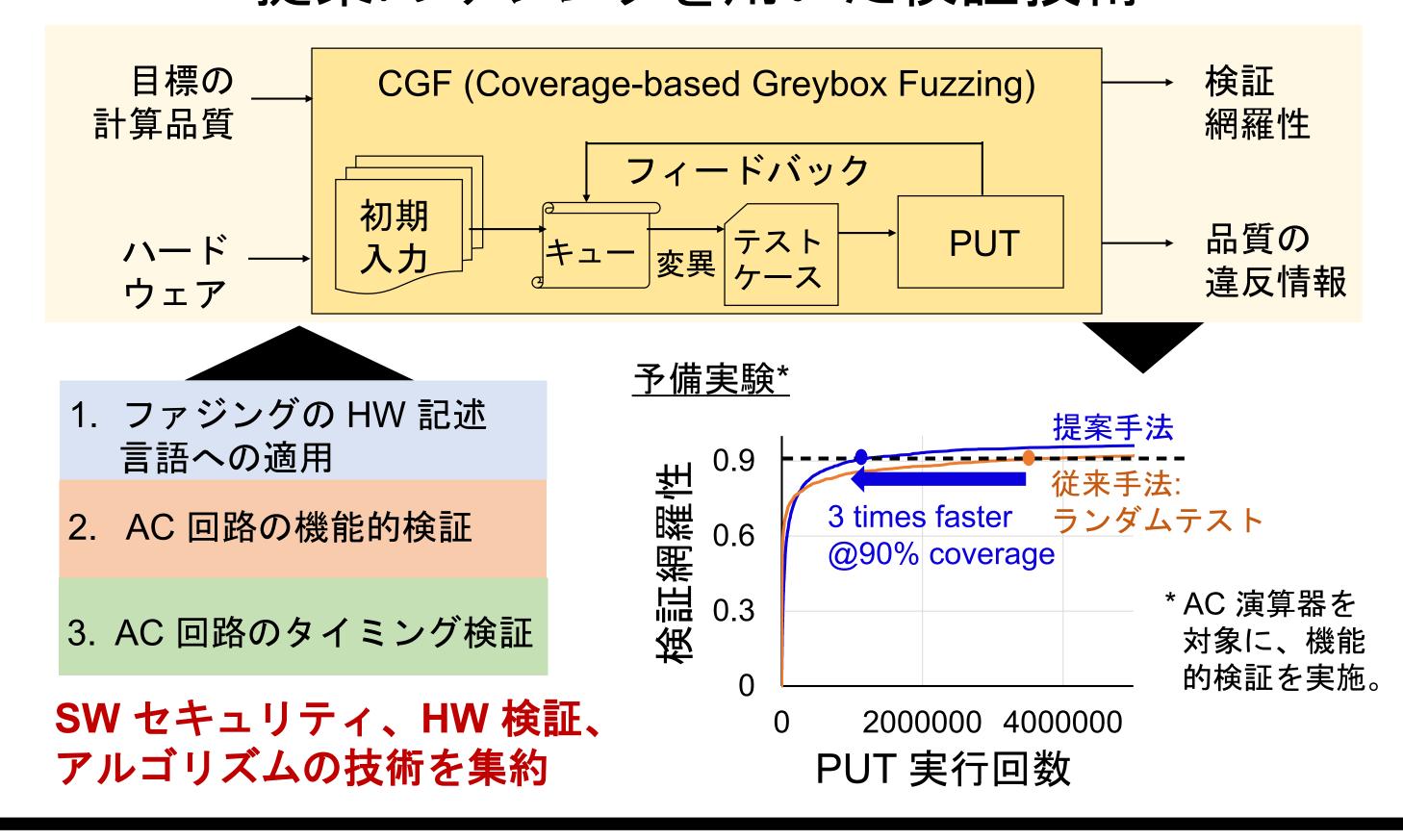

## AC回路の検証技術

提案: ファジングを用いた検証技術

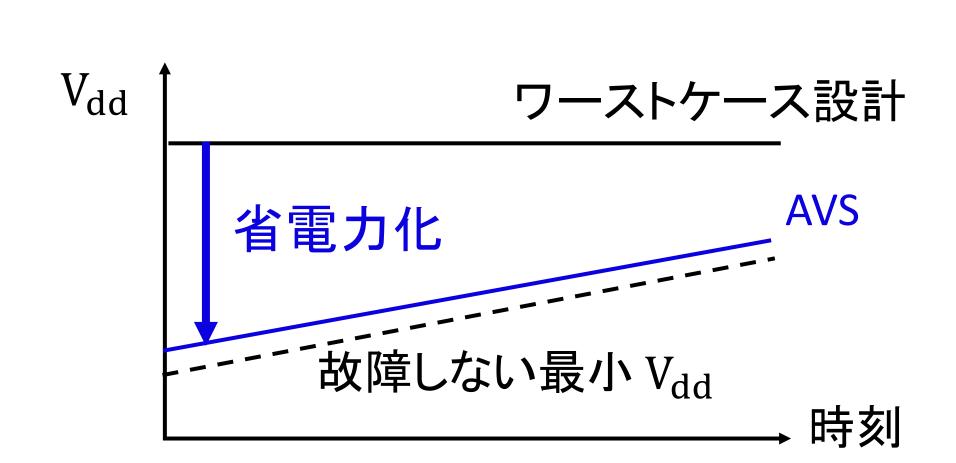

# 適応的電圧制御 (AVS)

チップの能力を引き出す設計パラダイム

# 目的: AVS 回路の設計と製造後テスト手法の確立

設計 性能評価 (既存技術を活用)

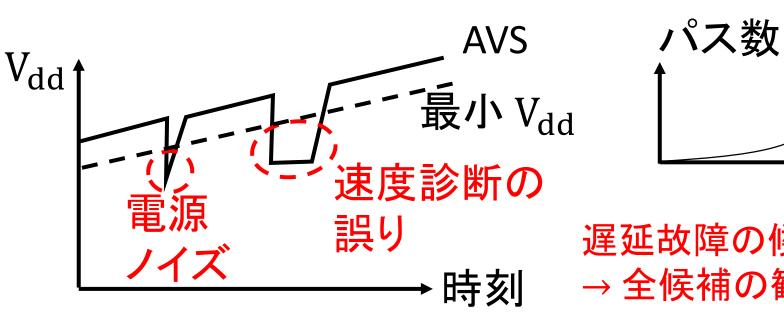

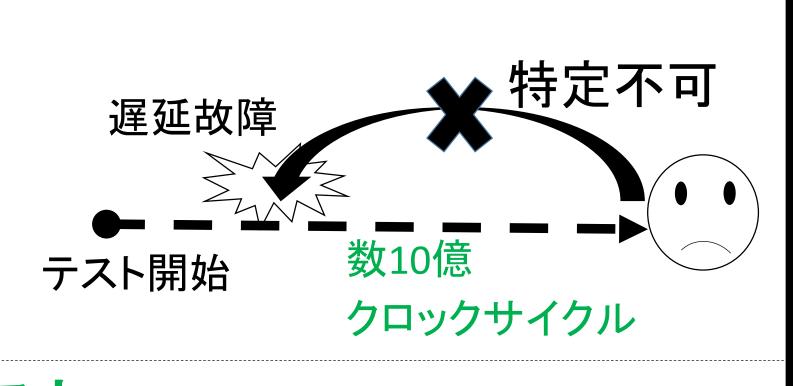

製造後テスト 課題: 故障の位置特定

実測評価

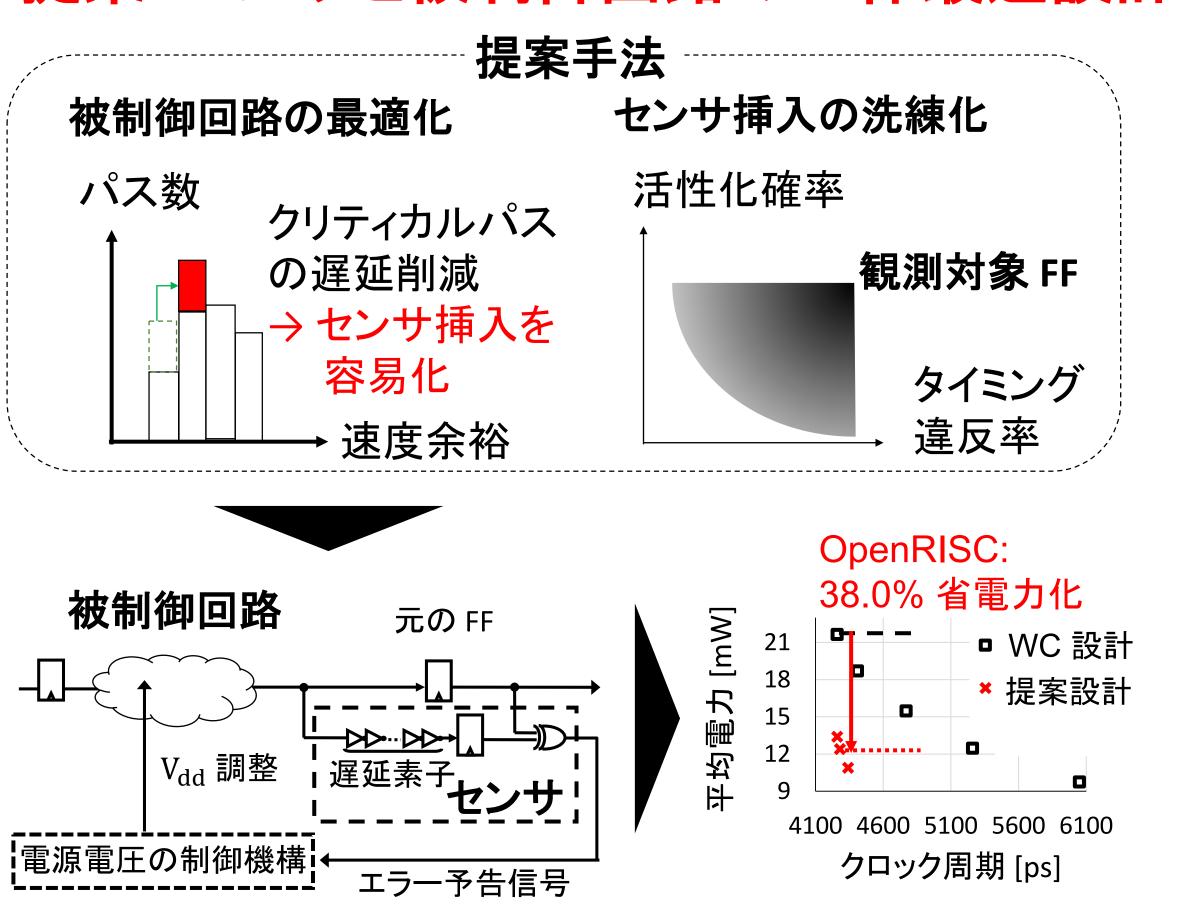

課題:電源電圧の適切な制御

パス 遅延故障の候補が膨大 →全候補の観測は非現実的

初期化

sha

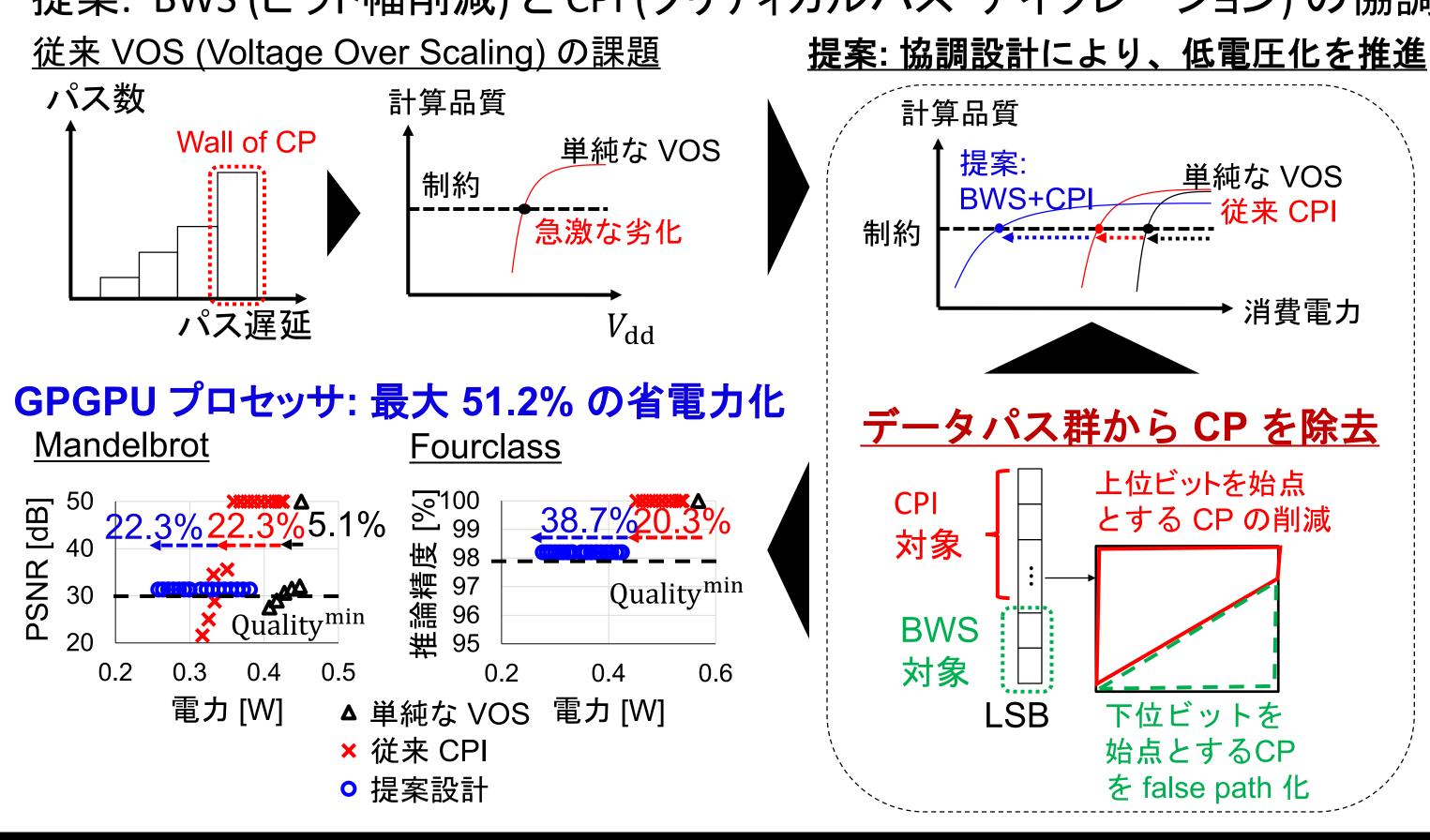

## AVSの設計

#### 提案: センサと被制御回路の一体最適設計

#### AVS のテスト

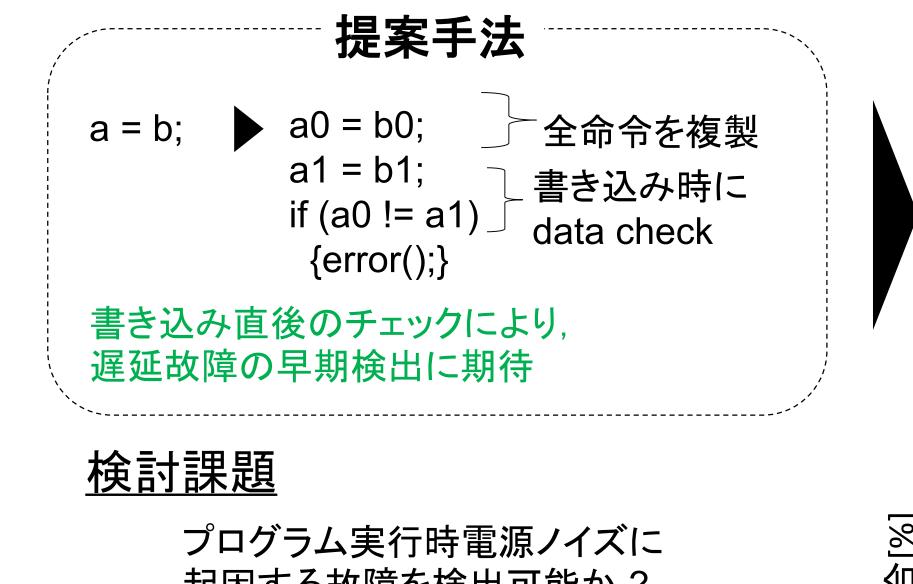

#### 提案: ソフトウェアベース故障検出手法

製造後テストプログラムに、故障の高速検出性を付与

結果 観測 DC 電源 評価ボード 未検出 検出 100 56.0 % : crc 早期検出 dijkstra silient error ~1000 1001~ 故障検出時間 [clock cycle]

対象回路:東芝 MeP

V<sub>dd</sub> 供給、

(65-nm 試作チップ)

起因する故障を検出可能か?

オリジナルミグ 複製前後で 同等の電源ノイズ 複製 → チェック機能しない チェック